VOL. 10, NO. 9, MAY 2015 ISSN 1819-6608

#### ARPN Journal of Engineering and Applied Sciences

© 2006-2015 Asian Research Publishing Network (ARPN). All rights reserved.

www.arpnjournals.com

# A VLSI APPROACH FOR DISTORTION CORRECTION IN SURVEILLANCE CAMERA IMAGES

M. Mohankumar<sup>1</sup>, V. Gopalakrishnan<sup>2</sup> and S.Yasotha<sup>1</sup>

<sup>1</sup>Anna University of Technology, Coimbatore, India

<sup>2</sup>Department of Electrical and Electronics Engineering, Government College of Technology, Coimbatore, India

#### ABSTRACT

An efficient VLSI architecture implementation for barrel distortion correction in surveillance camera images is presented. The distortion correction model is based on least squares estimation method. To reduce the computing complexity, an odd-order polynomial to approximate the back-mapping expansion polynomial is used. By algebraic transformation, the approximated polynomial becomes a monomial form which can be solved by Horner's algorithm. The proposed VLSI architecture can achieve frequency 218MHz with 1490 logic elements by using 0.18µm technology. Compared with previous techniques, the circuit reduces the hardware cost and the requirement of memory usage.

Keywords: VLSI, barrel distortion correction, least squares estimation, surveillance, horner's algorithm.

#### 1. INTRODUCTION

Nowadays, surveillance camera is commonly used in public and private places such as government buildings, military bases, car parks, and banks, and so forth. Surveillance camera can capture the entire region of interest with cameras as few as possible if cameras with large field of view are adopted. Surveillance cameras are video cameras used for the purpose of observing an area. It is connected to a recording device or IP network, and may be watched by a guard. Cameras and recording equipment used to be relatively expensive and required human personnel to monitor camera footage, but analysis of footage has been made easier by automated software that organizes digital video footage into a searchable database, and by video analysis software. The amount of footage is also drastically reduced by motion sensors which only record when motion is detected. With cheaper production techniques, surveillance cameras are simple and inexpensive enough to be used in home security systems, and for everyday surveillance.

The distortion correction circuit may be included in end-user camera equipment's, so how to implement it with lower hardware cost is an important issue. To reduce more hardware, algebraic transformation is used to replace all the vector magnitude square by a new variable. It makes the new combined polynomial becomes a monomial form. Therefore, Horner's algorithm [6] is able to efficiently evaluate the results of back-mapping and polar to Cartesian coordinate transformation. This approach not only greatly decreases the calculation complexity of back mapping but also provides a flexible architecture for different designs by time multiplexed technique [7], [8]. To reduce more hardware costs and power consumption, we also implemented a low cost linear interpolation circuit by algebraic manipulation technique. It greatly eliminates the number of multipliers from eight to three. In this paper, a low- cost, low-power, and low memory requirement distortion correction circuit is designed for surveillance or wide-angle camera applications.

# 2. OVERVIEW OF DISTORTION CORRECTION TECHNIQUE

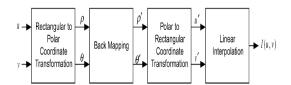

In this section, least-square estimation method is used for distortion correction technique. Barrel distortion can be corrected by two main tasks: 1) back mapping of all pixels in CIS onto DIS, and 2) calculating the intensity of every pixel in CIS by linear interpolation [7]. The block diagram of the distortion correction procedure is shown in Fig1. First the transformation mapping from rectangular coordinate to polar coordinate for all pixels is done. Then, a back mapping procedure is introduced to decrease the computing complexity and polar to rectangular coordinate steps by eliminating the angle  $\theta$  and reducing the square root operation for  $\rho$ . Finally, a basic algebraic manipulation is used to decrease the arithmetic resource of the linear interpolation.

**Figure-1**. Block diagram for distortion correction procedure.

The first step of the proposed distortion correction technique is transforming all pixels in the distorted image space (DIS) onto the corrected image space (CIS) i, e., this step is to convert rectangular to polar coordinate. The distortion center is  $(u^c, v^c)$  in DIS and the correction center is  $(u_c, v_c)$  in CIS. In DIS,  $(u^c, v^c)$  is the Cartesian coordinate and  $(\rho^c, \theta^c)$  is the polar coordinate. The distance  $\rho^c$  from distortion center  $(u^c, v^c)$  to an image pixel  $(u^c, v^c)$  and the angle  $\theta^c$  between the pixel and distortion center are given by

$$\rho' = \sqrt{(u' - u_c')^2 + (v' - v_c')^2}$$

(1)

## ARPN Journal of Engineering and Applied Sciences

© 2006-2015 Asian Research Publishing Network (ARPN). All rights reserved.

(12)

# www.arpnjournals.com

$$\theta' = arc \tan \left( \frac{v' - v_{lc}}{u' - u_{lc}} \right) \tag{2}$$

The distance  $\rho$  from distortion center ( $u_c$ ,  $v_c$ ) to an image pixel (u, v) and the angle  $\theta$  between the pixel and distortion center are given by

$$\rho = \sqrt{(u - u_c)^2 + (v - v_c)^2} \tag{3}$$

$$\theta = \arctan\left(\frac{v - v_c}{u - u_c}\right) \tag{4}$$

The second step is back-mapping process which will map the pixel  $(\rho, \theta)$  in CIS to  $(\rho', \theta')$  in DIS. The back mapping procedure can be defined by a back mapping expansion polynomial of degree N as

$$\rho' = \sum_{n=1}^{N} b_n p^n \tag{5}$$

where  $b_n$  is the back mapping coefficient which can be obtained by the least-squares estimation method.

The third step is to perform the polar to rectangular coordinate conversion. The location  $(u',\,v')$  in DIS can be calculated as

$$u' = u'_{c} + \rho' cos\theta'$$

$$v' = v'_{c} + \rho' sin\theta'$$

(7)

The next step is to perform linear interpolation. Here, the pixel (u', v') location need not be an integer location. Its intensity value can be calculated by linearly interpolating with the intensity values of the four neighboring pixels (u', v') around in DIS.

## Simplified back-mapping procedure

As mentioned above, the odd order polynomial is high-approximation to the back mapping expansion polynomial is used. The back mapping expansion polynomial can be approximated to odd-order polynomial as

$$\rho' = c_0 \rho + c_1 \rho^3 + c_2 \rho^5 + c_3 \rho^7 + \cdots.$$

(8)

where c0, c1, c2, c3... are back-mapping coefficients of the odd-order back-mapping polynomial. There are two steps to reduce the computing resources of back-mapping procedure. The first is eliminating the calculation of  $\theta$ . According to (7), the  $\theta$  and  $\theta$ ' are the same. Thus, the  $\cos\theta$  and  $\sin\theta$  can be obtained as

$$\sin \theta = \sin \theta = \frac{\mathbf{v} - \mathbf{v_c}}{\rho} \tag{9}$$

$$\cos \theta = \cos \theta = \frac{u - u_c}{\rho} \tag{10}$$

In below equations mentioned, here no odd power of  $\rho$  exists, so the square-root calculation for  $\rho$  can be removed.

$$u' = u'_c + \rho'$$

.  $\frac{u - u_c}{\rho}$

$$u' = u_c' + (c_0 + c_1 \rho^2 + c_2 \rho^4 + c_3 \rho^6 \dots \dots)^{\frac{1}{2}} \cdot (u - u_c)^{\frac{1}{2}}$$

(11)

$$v' = v_c' + \rho' \cdot \frac{v - v_c}{\rho}$$

$$v^{\parallel} = v_c^{\parallel} + (c_0 + c_1 \rho^2 + c_2 \rho^4 + c_3 \rho^6 \dots )^{\parallel} (v - v_c)^{\parallel}$$

Thus, the complex square-root calculation is eliminated because both u'and v'are calculated with  $\rho$  <sup>2</sup>rather than with  $\rho$ .

#### 3. HORNER'S ALGORITHM

The main purpose of Horner's algorithm [16] is to efficiently evaluate the polynomials in monomial form. Given the polynomial

where  $a_0$ ,  $a_1$ ,..., $a_n$  real numbers, then to evaluate the polynomial at a specific value of x, say  $x_0$ . A new sequence of constants is defined as follows:

$$b_{n} := a_{n}$$

$$b_{n-1} := a_{n-1} + b_{n}x_{0}$$

$$\vdots$$

$$b_{0} := a_{0} + b_{1}x_{0}.$$

(14)

Then  $b_0$  is the value of  $p(x_0)$

Then the polynomial can be written as

$$p(x) = a_0 + x(a_1 + x(a_2 + \cdots + x(a_{n-1} + a_n x) \cdots)).$$

(15)

Thus, by iteratively substituting the b<sub>i</sub> into the expression,

$$p(x_0) = a_0 + x_0(a_1 + x_0(a_2 + \dots + x_0(a_{n-1} + b_n x_0) \dots))$$

$$= a_0 + x_0(a_1 + x_0(a_2 + \dots + x_0(b_{n-1}) \dots))$$

$$\vdots$$

$$= a_0 + x_0(b_1)$$

$$= b_0.$$

(16)

As described above, an iteration function is used to rewrite the polynomial. The function  $p^n$  which is the *n*th iteration of p can be represented as  $p.p^{n-1}$  and it is defined as

#### ARPN Journal of Engineering and Applied Sciences

© 2006-2015 Asian Research Publishing Network (ARPN). All rights reserved.

#### www.arpnjournals.com

$$p^{n} = p. p^{n-1}$$

(17)

To rewrite the polynomial as iteration function, the evaluated polynomial at the specified value of  $x = x_0$  can be represented as

$$p(x_0) = (c_{n-1} + c_n \cdot x_0 \cdot p^{n-1}(x_0))$$

(18)

The polynomial is evaluated to compute  $p(x_o)$  where  $x_o$  is a constant.

The Horner's algorithm is executed by following the below steps:

**Step-1.** Set u = n (where n is the degree of the polynomial)

**Step-2.** Set Result = Cn.

**Step-3.** If u = 0 stop. Answer is Result.

**Step-4.** Compute Result = Result  $\times xo + Cu - 1$ .

**Step-5.** u = u - 1.

Step-6. Go to step 3.

By Horner's algorithm, the computing complexity of the evaluating polynomial can be decreased. The complexity of back mapping and polar to rectangular coordinate steps can be reduced in the same way.

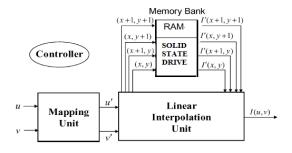

#### 4. PROPOSED VLSI ARCHITECTURE

Figure-2 shows the block diagram of proposed architecture. In this design, when the start signal is enabled, the circuit will output the intensity value of the first pixel after 21 clock cycles. Then, it can process one pixel in CIS per clock cycle. Totally, it would take (1024 x 728 + 21) cycles to process an image with 1024 x 728 pixels. This design consists of four main modules: mapping unit, memory bank, linear interpolation unit and controller. The memory bank is composed of solid state drives and RAM. The interpolation unit linearly interpolates the final intensity value. The controller provides the control signals of each state to other units and handles the whole correction procedure. The detailed circuits of mapping and linear interpolation units are described as follows.

Figure-2. Proposed VLSI architecture.

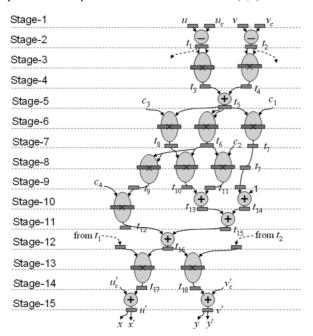

For each pixel (u, v) in CIS, the mapping unit performs the operations needed to calculate (u', v'). Most multipliers and adders are realized with 24-bit width as adopted in [6]. According to the simulation results obtained from XILINX, it was found that the propagation delay of a 24-bit multiplier is quite long. Hence, the 15-bit two-stage pipelined multiplier is adopted in the design to

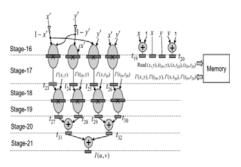

get better pipeline scheduling. Figure-3 shows the 15-stage pipelined architecture of the mapping unit. The linear interpolation unit obtains the intensity values of the four neighboring pixels around (u', v') and calculates the final intensity value I (u, v). Figure-4 shows the 6-stage pipelined architecture of the linear interpolation unit which performs the operations needed to calculate I (u,v).

Figure-3. 15-stage pipelined architecture of mapping unit.

**Figure-4.** 6-stage pipelined architecture of linear interpolation unit.

#### 5. RESULTS AND DISCUSSIONS

The VLSI architecture of the proposed design was implemented by using Verilog HDL. Here MATLAB is used to convert the image file to grey scale image. Table 1 shows the Simulation Results of two designs using Altera EP20K600EBC652-1X FPGA the size the design with TSMC's 0.18 m cell library. The results show that the design contains 1490 logic elements. It works with a clock period of 5 ns and operates at a clock rate of 218 MHz.

VOL. 10, NO. 9, MAY 2015 ISSN 1819-6608

#### ARPN Journal of Engineering and Applied Sciences

© 2006-2015 Asian Research Publishing Network (ARPN). All rights reserved.

#### www.arpnjournals.com

**Table-1.** Comparative analysis.

| Paper    | Logic elements | Clock rate | Throughput  |

|----------|----------------|------------|-------------|

| [11]     | 1686           | 200MHz     | 14Mpixels/s |

| Proposed | 1490           | 218MHz     | 21Mpixels/s |

#### 6. CONCLUSIONS

In this paper, a low-cost, low-power, and low memory requirement VLSI architecture of distortion correcting circuit was presented for surveillance images. The computing complexity of correcting functions is reduced by Horner's algorithm and the algebraic manipulation of the linear interpolation. This provides an efficient and effective approach to eliminate the distortion. It provides a logic element of about 1490, clock rate of 218MHz and throughput of 21Mpixels/s. From this it is proved that this algorithm has high performance than other existing VLSI correcting designs.

#### REFERENCES

- Anderson M. 1990. "VCR quality video at 1.5 Mbits/s," National Communication Forum, Chicago, October.

- [2] Coding of moving pictures and associated audio. Committee Draft of Standard ISO11172: ISO/MPEG 90/176, December. 1990.

- [3] Coding of moving pictures and associated audio. Committee Draft of Standard ISO11172: ISO/MPEG 90/176, December. 1990.

- [4] ITU-T and ISO/IEC JTC 1, "Generic coding of moving pictures and associated audio information – Part 2: Video," ITU-T Recommendation H.262 – ISO/IEC 13818-2 (MPEG-2), November. 1994.

- [5] I. Haritaoglu, D. Harwood and L. S. Davis. 2000. "W: Real-time surveillance of people and their activities," IEEE Trans. Pattern Anal. Machine Intell., Vol. 22, pp. 809–830, August.

- [6] Iain E. G. Richardson. 2003. "H.264 and MPEG-4 Video Compression: Video Coding for Nextgeneration Multimedia," John Wiley & Sons, Ltd.

- [7] H. T. Ngo and V. K. Asari. 2005."A pipelined architecture for real-time correction of barrel distortion in wide-angle camera images," IEEE Trans. Circuits Syst. Video Technol., Vol. 15, No. 3, pp. 436–444, March.

- [8] P. Y. Chen, C. C. Huang, Y. H. Shiau and Y. T. Chen. 2009. "A VLSI implementation of barrel distortion

- correction for wide-angle camera images," IEEE Trans. Circuits Syst. II Express Briefs, Vol. 56, No. 1, pp.51–55, January.

- [9] Jong Sun Kim, Dong Hae Yeom and Young Hoon Joo. 2011. "Fast and Robust Algorithm of Tracking Multiple Moving Objects for Intelligent Video Surveillance Systems". IEEE Transactions on Consumer Electronics, Vol. 57, No. 3, August.

- [10] Shih-Chia Huang. 2011. "An Advanced Motion Detection Algorithm with Video Quality Analysis for Video Surveillance Systems". IEEE Transactions on Circuits and Systems for Video Technology, Vol. 21, No. 1, January.

- [11] P. G. S. Mythili and S. Vamsee Krishna. 2013. "Time Multiplexed VLSI Architecture for Real-Time Barrel Distortion Correction in Video-Endoscopic Images", International Journal for Scientific Research & Development Vol. 1, No. 8.